Product Summary

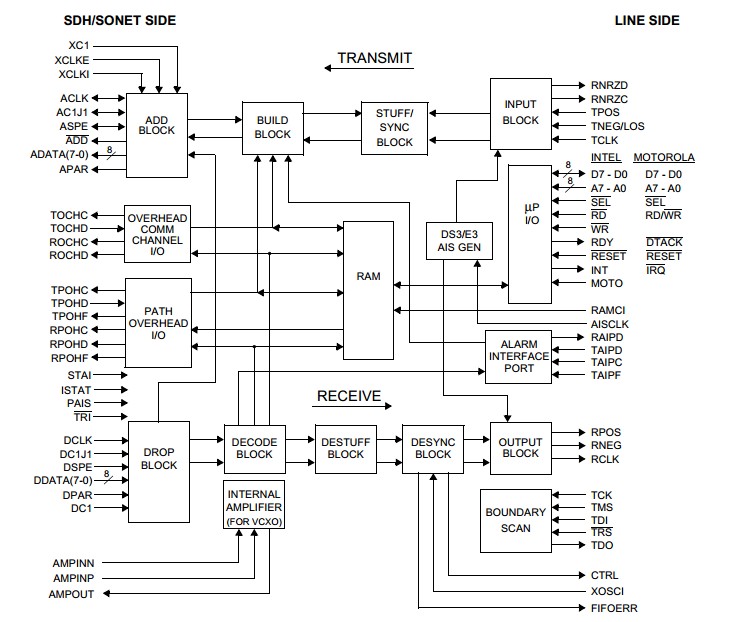

The TXC-03452CIOG is a level 3 mapper which maps a DS3 line signal into an STM-1 TUG-3 or STS-3/ STS-1 SPE or STS-1 SPE SDH/SONET signal. And it is mapped into an STM-1 TUG-3 signal only. The TXC-03452CIOG provides a TUG-3 formatted signal for STM-1 operation, or an STS SPE for STS-3 or STS-1 operation. The SDH/SONET signal is transmitted via an add bus with timing derived from the drop side, add side or from external timing (STS-1 only). An option is provided to generate the A1, A2 framing pattern, C1 byte and H1, H2 pointer towards the add bus when external timing mode is selected.

Parametrics

TXC-03452CIOG absolute maximum ratings:(1)Supply voltage VDD:-0.3V to +7.0 V; (2)DC input voltage:-0.5V to VDD + 0.5 V ; (3)Storage temperature range:-55°C to 150°C; (4)Ambient Operating Temperature:-40°C to 85°C; (5)Component Temperature x Time:270 x 5(°C x s); (6)Moisture Exposure Level:5 Level per EIA/JEDEC JESD22-A112-A; (7)Relative Humidity, during assembly:30% to 60 %; (8)Relative Humidity, in-circuit:0 to 100 %; (9)ESD Classification:absolute value 2000 V.

Features

TXC-03452CIOG features:(1)Maps DS3 (44.736 Mbit/s) or E3 (34.368 Mbit/s) line formats into SDH/SONET formats as follows: DS3 to/from STM-1/TUG-3;DS3 to/from STS-3/STS-1 SPE or STS-1 SPE;E3 to/from STM-1/TUG-3 only; (2)SDH/SONET bus access: Drop/add data byte access (with clock, C1J1, SPE,and parity); Add bus interface timing derived from drop bus, add bus, or external timing; (3) Path overhead byte processing: Microprocessor or external interface; B3 generation and detection with test mask; B3 performance counter (16-bit) and block error counter (8-bit); C2 mismatch and unequipped detection; G1 processing; FEBE count by block or bits (16-bit counter); (4)Microprocessor access: Motorola or Intel compatible (selected via a lead); Hardware/software interrupt capability; (5)Line Interface: Transmit and receive NRZ or rail operation with split operation capability; (6) Testing functions: SONET, facility, or line loopback; Boundary scan capability (IEEE 1149.1); (7)144-lead plastic quad flat package (PQFP) or 208-lead plastic ball grid array package (PBGA).

Diagrams

|

TXC-02030 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

TXC-02201 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

TXC-02302B |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

TXC-02623 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

TXC-03351 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

TXC-03361 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)