Product Summary

The MC9S12XS256MAL is a Microcontroller. The MC9S12XS256MAL will retain the low cost, power consumption, EMC and code-size efficiency advantages currently enjoyed by users of Freescale’s existing 16-Bit MC9S12 MCU Family. Based around an enhanced S12 core, the MC9S12XS256MAL will deliver 2 to 5 times the performance of a 25-MHz S12 whilst retaining a high degree of pin and code compatibility with the S12. The MC9S12XS256MAL introduces the performance boosting XGATE module. Using enhanced DMA functionality, this parallel processing module offloads the CPU by providing high-speed data processing and transfer between peripheral modules, RAM, Flash EEPROM and I/O ports. Providing up to 80 MIPS of performance additional to the CPU, the XGATE can access all peripherals, Flash EEPROM and the RAM block.

Parametrics

MC9S12XS256MAL absolute maximum ratings: (1)I/O, regulator and analog supply voltage VDD35: –0.3 to 6.0 V; (2)Digital logic supply voltage: -0.3 to 3.0V; (3)PLL supply voltage: -0.3 to 3.0V; (4)Voltage difference VDDX to VDDR and VDDA ΔVDDX: –0.3 to 0.3 V; (5)Voltage difference VSSX to VSSR and VSSA ΔVSSX: –0.3 to 0.3 V; (6)Digital I/O input voltage VIN: –0.3 to 6.0 V; (7)Analog reference VRH, VRL: –0.3 to 6.0 V; (8)XFC, EXTAL, XTAL inputs VILV: –0.3 to 3.0 V; (9)TEST input VTEST: –0.3 to 10.0 V; (10)Instantaneous maximum current Single pin limit for all digital I/O pins:-25 to 25mA.

Features

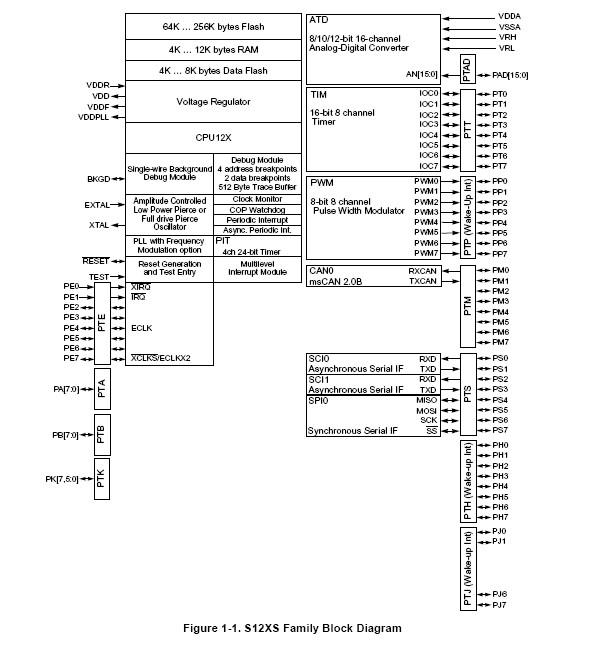

MC9S12XS256MAL features: (1)Upward compatible with MC9S12 instruction set; (2)Interrupt stacking and programmer’s model identical to MC9S12; (3)Instruction queue; (4)Enhanced indexed addressing; (5)Enhanced instruction set; (6)EBI (external bus interface); (7)MMC (module mapping control); (8)INT (interrupt controller); (9)DBG (debug module to monitor HCS12X CPU and XGATE bus activity); (10)BDM (background debug mode); (11)8 PWM (pulse-width modulator) channels; (12)Serial interfaces; (13)144-pin LQFP, 112-pin LQFP, and 80-pin QFP packages.

Diagrams

(Hong Kong)

(Hong Kong)